Topic: Revision 4 of the XT-IDE

Date: 2017 NOV 23

Update: Assembly Video Available!

Modern Classic has uploaded an XT-IDE rev 4 kit assembly video to YouTube! His process is basically the same sequence we use to assemble XT-IDEs in the shop. The video covers all of the basics and provides a more visually-oriented guide than any of the forum posts or writeups.

Quick Links

- GitHub Repository

- Build Thread on VC Forums

- Bare Boards on Tindie

- Parts Kits on Tindie

- Assembled Boards on Tindie

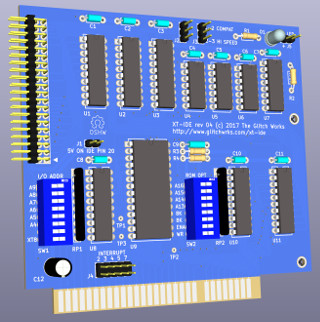

Changes

The XT-IDE rev 4 board is an improvement on the Glitch Works XT-IDE rev 3, which itself is a descendant of the original XT-IDE project from Jeff Leyda/Hargle and N8VEM/vintage-computer.com. As with the original project, the board is completely open source, licensed under the GNU GPL v3.0. It was designed with KiCad, a completely open source cross-platform EDA package. Here’s a 3D rendering of the prototype from KiCad:

The main changes are as follows:

- Better/more consistent parts numbering (U1 is top left, U2 is to the right, etc.)

- Thicker/more consistent silkscreen (some board houses produced illegible/broken silkscreen on some labels and symbols)

- Larger pads around some of the jumper headers

- Better pin 1 identification for ICs

- Rotate IC part number text (e.g. 74LS688) to match typical orientation on ICs

- Change bypass cap values to match parts kit (changed to C instead of a uF value)

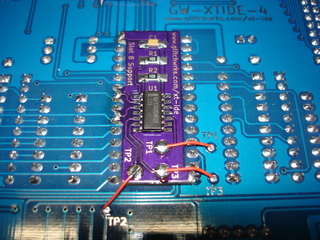

- Additional test points for Slot 8 Support installation

The above changes make assembly easier, especially for kit builders. The Slot 8 Support test points keep jumper wires short, and route *CARDSEL through SW1 position 8.

Latch Read/Write Timing

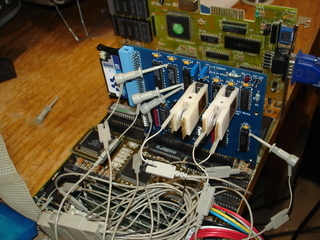

Alan Hightower ran into me at VCF East 2017 and described a race condition he encountered with the XT-IDE rev 3 while he was developing the NetPi-IDE. The basic issue was that the IDE device’s read/write lines were being de-asserted before the latch interface on IDE reads, and data from the latch interface wasn’t being held long enough on IDE writes. This issue seems to only occur with very fast IDE devices. During the prototyping phase, I hooked up the HP 1650A logic analyzer and took a look at what was going on:

With the analyzer hooked up, I was able to capture read and write timing. The following image shows various read line timing:

IORISA is the *IOR strobe essentially directly off of the ISA bus. IORIDE is the same signal after passing through four sections of a 74LS04 inverter, this adds around 20 nS of gate delay. HI RD is the latch strobe to U1, the high byte read latch that stores the upper 8 bits of the ATA device’s output data during a read, so we can grab it later. As seen in the timing diagram, where HI RD used to lag IORISA by 10 nS, it now leads by 10 nS due to the 20 nS delay chain. This means the latch stores its value 10 nS before the ATA device stops outputting valid data, which is well within the spec for even the 74LS573 latch (the kits typically come with 74F573 latches, because I have a supply of them).

Here’s the various write signal timings:

IOWIDE is the *IOW signal essentially directly off of the ISA bus. HI WR is the latch strobe for storing the upper byte before doing a 16-bit write to the ATA device. HI OUT is the delayed “2 signal” from the XT-IDE logic (I’ve since relabeled it *HI_BYTE_OUT on the schematic, which I think is clearer). It was delayed by running it through two sections of a 74LS04 inverter and one section of a 74LS32 OR gate, with one input of the OR gate tied to ground. As seen in the timing diagram, *HI_BYTE_OUT now de-asserts 10 nS after the *IOW line, ensuring that data is presented to the ATA device for 10 nS past the end of the ATA write operation. I’m not sure if many (or any) ATA devices are this picky about the timing, but correcting it at the same time as making other rev 4 changes didn’t require any spare gates.

All of this was breadboarded on an old XT-IDE rev 3 prototype board from the initial rev 3 design, with a 74LS04 dead-bugged onto the circuit board and wired in. I made the read delay chain modifications and had some more prototypes run. Alan has one of them, which he used to confirm that the read timing was fixed. I modified a second with a socket for the 74LS04 so that I could test faster devices, as well as adding in the high byte output delay. I tested 74S04, 74LS04, 7404, and 74F04 devices, to make sure that whatever got stuck in there by someone assembling an XT-IDE would provide sufficient delay. All provided sufficient delay, the 7404 was the only measurable difference, providing around 25 nS instead of 20 nS, which is fine.

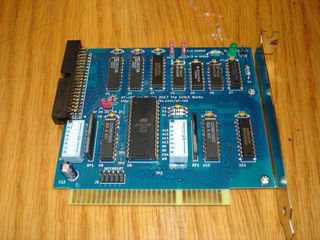

Production Boards

With the race conditions worked out, it was time to run production boards! The XT-IDE rev 4 boards were produced with the same specs as the XT-IDE rev 3 boards. Here’s a bare production board:

The boards were built up, tested, and works fine! In addition to building up a plain XT-IDE rev 4 board, I installed a Slot 8 Support module. The new test points make the Slot 8 Support even easier to install:

So, that’s the fourth revision of the Hargle/N8VEM XT-IDE! See the links at the top for the GitHub repository, build thread, and Tindie store links! Or, check out the Glitch Works Tindie Store for XT-IDE related listings and other projects.

hard drives replaced